- Magnetoresistive random access memory

-

Computer memory types Volatile - RAM

- In development

- Historical

Non-volatile - ROM

- Flash memory

- Early stage

- In development

- Historical

Magnetoresistive Random-Access Memory is a non-volatile computer memory (NVRAM) technology that has been under development since the 1990s. Continued increases in density of existing memory technologies – notably flash RAM and DRAM – kept it in a niche role in the market, but its proponents believe that the advantages are so overwhelming that magnetoresistive RAM will eventually become dominant for all types of memory, becoming a true universal memory.[1]

Contents

Description

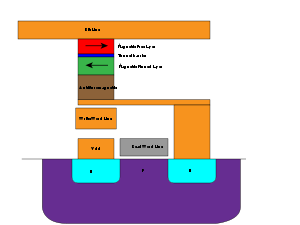

Unlike conventional RAM chip technologies, in MRAM data is not stored as electric charge or current flows, but by magnetic storage elements. The elements are formed from two ferromagnetic plates, each of which can hold a magnetic field, separated by a thin insulating layer. One of the two plates is a permanent magnet set to a particular polarity, the other's field can be changed to match that of an external field to store memory. This configuration is known as a spin valve and is the simplest structure for a MRAM bit. A memory device is built from a grid of such "cells".

The simplest method of reading is accomplished by measuring the electrical resistance of the cell. A particular cell is (typically) selected by powering an associated transistor that switches current from a supply line through the cell to ground. Due to the magnetic tunnel effect, the electrical resistance of the cell changes due to the orientation of the fields in the two plates. By measuring the resulting current, the resistance inside any particular cell can be determined, and from this the polarity of the writable plate. Typically if the two plates have the same polarity this is considered to mean "1", while if the two plates are of opposite polarity the resistance will be higher and this means "0".

Data is written to the cells using a variety of means. In the simplest, each cell lies between a pair of write lines arranged at right angles to each other, above and below the cell. When current is passed through them, an induced magnetic field is created at the junction, which the writable plate picks up. This pattern of operation is similar to core memory, a system commonly used in the 1960s. This approach requires a fairly substantial current to generate the field, however, which makes it less interesting for low-power uses, one of MRAM's primary disadvantages. Additionally, as the device is scaled down in size, there comes a time when the induced field overlaps adjacent cells over a small area, leading to potential false writes. This problem, the half-select (or write disturb) problem, appears to set a fairly large size for this type of cell. One experimental solution to this problem was to use circular domains written and read using the giant magnetoresistive effect, but it appears this line of research is no longer active.

Another approach, the toggle mode, uses a multi-step write with a modified multi-layer cell. The cell is modified to contain an "artificial antiferromagnet" where the magnetic orientation alternates back and forth across the surface, with both the pinned and the free layers, consisting of multi-layer stacks isolated by a thin "coupling layer". The resulting layers have only two stable states, which can be toggled from one to the other by timing the write current in the two lines so one is slightly delayed, thereby "rotating" the field. Any voltage less than the full write level actually increases its resistance to flipping. That means that other cells located along one of the write lines will not suffer from the half-select problem, allowing for smaller cell sizes.

A newer technique, spin-transfer torque (STT) or Spin Transfer Switching, uses spin-aligned ("polarized") electrons to directly torque the domains. Specifically, if the electrons flowing into a layer have to change their spin, this will develop a torque that will be transferred to the nearby layer. This lowers the amount of current needed to write the cells, making it about the same as the read process.[2] There are concerns that the "classic" type of MRAM cell will have difficulty at high densities due to the amount of current needed during writes, a problem STT avoids. For this reason, the STT proponents expect the technique to be used for devices of 65 nm and smaller.[citation needed] The downside is the need to maintain the spin coherence. Overall, the STT requires much less write current than conventional or toggle MRAM. Research in this field indicates that STT current can be reduced up to 50 times by using a new composite structure. [3] However, higher speed operation still requires higher current.[4]

Other potential arrangements include "Thermal Assisted Switching" (TAS-MRAM), which briefly heats up (reminiscent of phase-change memory) the magnetic tunnel junctions during the write process and keeps the MTJs stable at a colder temperature the rest of the time;[5] and "vertical transport MRAM" (VMRAM), which uses current through a vertical column to change magnetic orientation, a geometric arrangement that reduces the write disturb problem and so can be used at higher density. [6]

Comparison with other systems

Density

The main determinant of a memory system's cost is the density of the components used to make it up. Smaller components, and fewer of them, mean that more "cells" can be packed onto a single chip, which in turn means more can be produced at once from a single silicon wafer. This improves yield, which is directly related to cost.

DRAM uses a small capacitor as a memory element, wires to carry current to and from it, and a transistor to control it – referred to as a "1T1C" cell. This makes DRAM the highest-density RAM currently available, and thus the least expensive, which is why it is used for the majority of RAM found in a computer.

MRAM is physically similar to DRAM in makeup, although often does not require a transistor for the write operation. However, as mentioned above, the most basic MRAM cell suffers from the half-select problem, which limits cell sizes to around 180 nm or more. Toggle-mode MRAM offers a much smaller size before this becomes a problem, apparently around 90 nm,[7] the same size as most current DRAM products. To be worth putting into wide production, however, it is generally believed that MRAM will have to move to the 65 nm size of the most advanced memory devices, which will require the use of STT.

Power consumption

Since the capacitors used in DRAM lose their charge over time, memory assemblies that use DRAM must refresh all the cells in their chips approximately 20 times a second, reading each one and re-writing its contents. As DRAM cells decrease in size, the refresh cycles become shorter, and the power-draw more continuous.

In contrast, MRAM never requires a refresh. This means that not only does it retain its memory with the power turned off but also there is no constant power-draw. While the read process in theory requires more power than the same process in a DRAM, in practice the difference appears to be very close to zero. However, the write process requires more power in order to overcome the existing field stored in the junction, varying from three to eight times the power required during reading.[8][9] Although the exact amount of power savings depends on the nature of the work – more frequent writing will require more power – in general MRAM proponents expect much lower power consumption (up to 99% less) compared to DRAM. STT-based MRAMs eliminate the difference between reading and writing, further reducing power requirements.

It is also worth comparing MRAM with another common memory system, flash RAM. Like MRAM, flash does not lose its memory when power is removed, which makes it very common as a "hard disk replacement" in small devices such as digital audio players or digital cameras. When used for reading, flash and MRAM are very similar in power requirements. However, flash is re-written using a large pulse of voltage (about 10 V) that is stored up over time in a charge pump, which is both power-hungry and time-consuming. In addition, the current pulse physically degrades the flash cells, which means flash can be written only to some finite number of times before it must be replaced.

In contrast, MRAM requires only slightly more power to write than read, and no change in the voltage, eliminating the need for a charge pump. This leads to much faster operation, lower power consumption, and an indefinitely long "lifetime".

Performance

DRAM performance is limited by the rate at which the charge stored in the cells can be drained (for reading) or stored (for writing). MRAM operation is based on measuring voltages rather than charges or currents, so there is less "settling time" needed. IBM researchers have demonstrated MRAM devices with access times on the order of 2 ns, somewhat better than even the most advanced DRAMs built on much newer processes.[10] A team at the German Physikalisch-Technische Bundesanstalt have demonstrated MRAM devices with 1 ns settling times, better than the currently accepted theoretical limits for DRAM, although the demonstration was a single cell.[11] The differences compared to flash are far more significant, with write times as much as thousands of times faster.

The only current memory technology that easily competes with MRAM in terms of performance is static RAM, or SRAM. SRAM consists of a series of transistors arranged in a flip-flop, which will hold one of two states as long as power is applied. Since the transistors have a very low power requirement, their switching time is very low. However, since an SRAM cell consists of several transistors, typically four or six, its density is much lower than DRAM. This makes it expensive, which is why it is used only for small amounts of high-performance memory, a notable one being the CPU cache in almost all modern CPU designs.

Although MRAM is not quite as fast as SRAM, it is close enough to be interesting even in this role. Given its much higher density, a CPU designer may be inclined to use MRAM to offer a much larger but somewhat slower cache, rather than a smaller but faster one. It remains to be seen how this trade-off will play out in the future.

Overall

MRAM has similar performance to SRAM, similar density of DRAM but much lower power consumption than DRAM, and is much faster and suffers no degradation over time in comparison to flash memory. It is this combination of features that some suggest make it the "universal memory", able to replace SRAM, DRAM, EEPROM, and flash. This also explains the huge amount of research being carried out into developing it.

However, to date, MRAM has not been widely adopted in the market. It may be that vendors are not prepared to take the risk of allocating a modern fab to MRAM production when such fabs cost upwards of a few billion dollars to build and can instead generate revenue by serving developed markets producing flash and DRAM memories.

The very latest fabs seem to be used for flash, for example producing 16 Gbit parts produced by Samsung on a 50 nm process.[12] Slightly older fabs are being used to produce most DDR2 DRAM, most of which is produced on a one-generation-old 90 nm process rather than using up scarce leading-edge capacity.

In comparison, MRAM is still largely "in development", and being produced on older non-critical fabs. The only commercial product widely available at this point is Everspin's 4 Mbit part, produced on a several-generations-old 180 nm process. As demand for flash continues to outstrip supply, it appears that it will be some time before a company can afford to "give up" one of their latest fabs for MRAM production. Even then, MRAM designs currently do not come close to flash in terms of cell size, even using the same fab.[citation needed]

History

Most of the following has been taken from mram-info web site:

- 1955 - Magnetic core memory had the same reading writing principle as MRAM

- 1988 - European scientists (Albert Fert and Peter Grünberg) discovered the "giant magnetoresistive effect" in thin-film structures.

- 1995 - Motorola (later to become Freescale) initiates work on MRAM development

- 2000 - IBM and Infineon established a joint MRAM development program.

- 2000 - Spintec laboratory's first Spin Torque Transfer patent.

- 2002 - NVE Announces Technology Exchange with Cypress Semiconductor.

- 2003 - A 128 kbit MRAM chip was introduced, manufactured with a 180 nm lithographic process

2004

- June - Infineon unveiled a 16-Mbit prototype, manufactured with a 180 nm lithographic process

- September - MRAM becomes a standard product offering at Freescale.

- October - Taiwan developers of MRAM tape out 1 Mbit parts at TSMC.

- October - Micron drops MRAM, mulls other memories.

- December - TSMC, NEC, Toshiba describe novel MRAM cells.

- December - Renesas Technology trumpets a high performance, high-reliability MRAM technology.

- Spintech laboratory's first observation of Thermal Assisted Switching (TAS) as MRAM approach.

- Crocus Technology is founded; the company is a developer of second-generation MRAM

2005

- January - Cypress Semiconductor samples MRAM, using NVE IP.

- March - Cypress to Sell MRAM Subsidiary.

- June - Honeywell posts data sheet for 1-Mbit rad-hard MRAM using a 150 nm lithographic process

- August - MRAM record: memory cell runs at 2 GHz.

- November - Renesas Technology and Grandis collaborate on development of 65 nm MRAM employing spin torque transfer (STT).

- November - NVE receives an SBIR grant to research cryptographic tamper-responsive memory.[13]

- December - Sony announced the first lab-produced spin-torque-transfer MRAM, which utilizes a spin-polarized current through the tunneling magnetoresistance layer to write data. This method consumes less power and is more scalable than conventional MRAM. With further advances in materials, this process should allow for densities higher than those possible in DRAM.

- December - Freescale Semiconductor Inc. demonstrates an MRAM that uses magnesium oxide, rather than an aluminum oxide, allowing for a thinner insulating tunnel barrier and improved bit resistance during the write cycle, thereby reducing the required write current.

- Spintec laboratory gives Crocus Technology exclusive license on its patents.

Current status

2006

- February - Toshiba and NEC announced a 16 Mbit MRAM chip with a new "power-forking" design. It achieves a transfer rate of 200 MB/s, with a 34 ns cycle time - the best performance of any MRAM chip. It also boasts the smallest physical size in its class — 78.5 square millimeters — and the low voltage requirement of 1.8 volts.[14]

- July - On July 10, Austin Texas - Freescale Semiconductor begins marketing a 4-Mbit MRAM chip, which sells for approximately $25.00 per chip.[15]

2007

- R&D moving to spin transfer torque RAM (SPRAM)

- February - Tohoku University and Hitachi developed a prototype 2 Mbit Non-Volatile RAM Chip employing spin-transfer torque switching.[16]

- August - "IBM, TDK Partner In Magnetic Memory Research on Spin Transfer Torque Switching" IBM and TDK to lower the cost and boost performance of MRAM to hopefully release a product to market.[17]

- November - Toshiba applied and proved the spin transfer torque switching with perpendicular magnetic anisotropy MTJ device.[18]

- November - NEC Develops World's Fastest SRAM-Compatible MRAM With Operation Speed of 250 MHz.[19]

2008

- Japanese satellite, SpriteSat, to use Freescale MRAM to replace SRAM and FLASH components [20]

- June - Samsung and Hynix become partner on STT-MRAM [1]

- June - Freescale spins off MRAM operations as new company Everspin [2]

- August - Scientists in Germany have developed next-generation MRAM that is said to operate as fast as fundamental performance limits allow, with write cycles under 1 nanosecond.

2009

- June - Hitachi and Tohoku University demonstrated a 32-Mbit spin-transfer torque RAM (SPRAM).[3]

- June - Crocus Technology and Tower Semiconductor announce deal port Crocus' MRAM process technology to Tower's manufacturing environment[21]

2010

- June - Hitachi and Tohoku Univ announced Multi-level SPRAM [4]

2011- March - PTB, Germany, announces having achieved a below 500 ps (2GBit/s) write cycle[22]

Applications

Proposed uses for MRAM include devices such as:

- Aerospace and military systems

- Digital cameras

- Notebooks

- Smart cards

- Mobile telephones

- Cellular base stations

- Personal Computers

- Battery-Backed SRAM replacement

- Datalogging specialty memories (black box solutions)

- Media players

- Book readers

See also

- Magnetic bubble memory

- EEPROM

- FeRAM

- Ferromagnetism

- Magnetoresistance

- Memristor

- NRAM

- nvSRAM

- Phase-change memory (PRAM)

- MOSFET

- Spin valve

- Tunnel magnetoresistance

- Spin transfer torque

- Freescale Semiconductor

- Crocus Technology

References

- ^ Johan Åkerman, "Toward a Universal Memory", Science, Vol. 308. no. 5721 (22 April 2005), pp. 508 - 510, DOI: 10.1126/science.1110549

- ^ "Renesas, Grandis to Collaborate on Development of 65 nm MRAM Employing Spin Torque Transfer", 1 December 2005

- ^ "Lower Switching Current for Spin-Torque Transfer in Magnetic Storage Devices such as Magnetoresistive Random Access Memory (MRAM)". University of Minnesota. http://www.license.umn.edu/Products/Lower-Switching-Current-for-Spin-Torque-Transfer-in-Magnetic-Storage-Devices-such-as-Magetoresistive-Random-Access-Memory-%28MRAM%29__Z09007.aspx. Retrieved 15 August 2011.

- ^ Y. Huai, AAPPS Bulletin, December 2008, vol. 18, no. 6, p.33, "Spin-Transfer Torque MRAM (STT-MRAM): Challenges and Prospects."

- ^ http://www.crocus-technology.com/pdf/BH GSA Article.pdf

- ^ "How MRAM Works"

- ^ "Magnetoresistive Random Access Memory", Freescale Semiconductor, 23 June 2006

- ^ William J. Gallagher and Stuart S. P. Parkin, "Development of the magnetic tunnel junction MRAM at IBM: From first junctions to a 16-Mb MRAM demonstrator chip", IBM, 24 January 2006

- ^ Rajagopalan Desikan et all, [http://www.research.ibm.com/people/l/lefurgy/Publications/mram-tr2002-47.pdf "On-chip MRAM as a High-Bandwidth, Low-Latency Replacement for DRAM Physical Memories"], Department of Computer Sciences, University of Texas at Austin, 27 September 2002

- ^ "Past, Present and Future of MRAM", NIST Magnetic Technology, 22 July 2003

- ^ Kate McAlpine, "Spin flip trick points to fastest RAM yet", NewScientist, 13 August 2008

- ^ "SAMSUNG Samples First 50-nanometer 16Gb NAND Flash for Solid State Disk and Other High-density Applications" (Press release). Samsung. 2007-01-03. http://www.samsung.com/PressCenter/PressRelease/PressRelease.asp?seq=20070103_0000309157. Retrieved 2007-01-03.

- ^ SBIR Phase I: Zero-Remanence Tamper-Responsive Cryptokey Memory

- ^ "Toshiba and NEC Develop World's Fastest, Highest Density MRAM" (Press release). NEC Corporation. 2006-02-07. http://www.nec.co.jp/press/en/0602/0702.html. Retrieved 2006-07-10.

- ^ "Freescale Leads Industry in Commercializing MRAM Technology" (Press release). Freescale Semiconductor. 2006-07-10. http://media.freescale.com/phoenix.zhtml?c=196520&p=irol-newsArticle&ID=880030. Retrieved 2006-07-10.

- ^ "Prototype 2 Mbit Non-Volatile RAM Chip Employing Spin-Transfer Torque Writing Method" (Press release). Hitachi Ltd.. 2007-02-13. http://www.hitachi.com/New/cnews/070213.html. Retrieved 2007-02-13.

- ^ "IBM and TDK Launch Joint Research & Development Project for Advanced MRAM" (Press release). IBM. 2007-08-19. http://www-03.ibm.com/press/us/en/pressrelease/22180.wss. Retrieved 2007-08-22.

- ^ "Toshiba develops new MRAM device that opens the way to giga-bits capacity" (Press release). Toshiba Corporation. 2007-11-06. http://www.toshiba.co.jp/about/press/2007_11/pr0601.htm. Retrieved 2007-11-06.

- ^ "NEC Develops World's Fastest SRAM-Compatible MRAM With Operation Speed of 250MHz." (Press release). NEC Corporation. 2007-11-30. http://www.nec.co.jp/press/en/0711/3001.html. Retrieved 2007-12-01.

- ^ Japanese Satellite First to Use Magnetic Memory: Scientific American

- ^ http://www.crocus-technology.com/pr-06-18-09.html

- ^ "Extremely fast MRAM data storage within reach" (Press release). PTB. 2011-03-08. http://www.ptb.de/en/aktuelles/archiv/presseinfos/pi2011/pitext/pi110308.html. Retrieved 2011-03-09.

External links

- www.mram-info.com, a clearinghouse of MRAM industry news

- IBM research - MRAM By Richard Butner

- Science magazine article from April, 2005

- Science magazine article from September, 2005

- Wired News article from February, 2006

- NEC Press Release from February, 2006

- BBC news article from July, 2006

- Freescale MRAM - an in-depth examination from August 2006

- MRAM – The Birth of the Super Memory - An article and an interview with Freescale about their MRAM technology

- Spin torque applet - An applet illustrating the principles underlying spin-torque transfer MRAM

- New Speed Record for Magnetic Memories - The Future of Things article

Magnetic storage media Wire (1898) • Tape (1928) • Drum (1932) • Ferrite core (1949) • Hard disk (1956) • Stripe card (1956) • MICR (1956) • Thin film (1962) • CRAM (1962) • Twistor (~1968) • Floppy disk (1969) • Bubble (~1970) • MRAM (1995) • Racetrack (2008)

Wikimedia Foundation. 2010.