- Semiconductor device fabrication

-

Semiconductor

manufacturing

processes

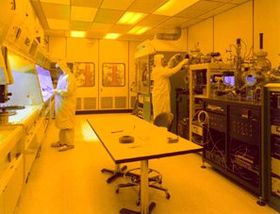

Half-nodes NASA's Glenn Research Center cleanroom.

NASA's Glenn Research Center cleanroom.

Semiconductor device fabrication is the process used to create the integrated circuits that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photolithographic and chemical processing steps during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

The entire manufacturing process, from start to packaged chips ready for shipment, takes six to eight weeks and is performed in highly specialized facilities referred to as fabs.

Contents

History

Main article: Integrated circuitWhen feature widths were far greater than about 10 micrometres, purity was not the issue that it is today in device manufacturing. As devices became more integrated, cleanrooms became even cleaner. Today, the fabs are pressurized with filtered air to remove even the smallest particles, which could come to rest on the wafers and contribute to defects. The workers in a semiconductor fabrication facility are required to wear cleanroom suits to protect the devices from human contamination.[1]

In an effort to increase profits, semiconductor device manufacturing has spread from Texas and California in the 1960s to the rest of the world, such as Europe, Middle East, and Asia. It is a global business today.[citation needed]

The leading semiconductor manufacturers typically have facilities all over the world. Intel, the world's largest manufacturer, has facilities in Europe and Asia as well as the U.S. Other top manufacturers include Taiwan Semiconductor Manufacturing Company (Taiwan), STMicroelectronics (Europe), Analog Devices (US), Integrated Device Technology (US), Atmel (US/Europe), Freescale Semiconductor (US), Samsung (Korea), Texas Instruments (US), IBM (US), GlobalFoundries (Germany, Singapore, future New York fab in construction), Toshiba (Japan), NEC Electronics (Japan), Infineon (Europe), Renesas (Japan), Fujitsu (Japan/US), NXP Semiconductors (Europe and US), Micron Technology (US), Hynix (Korea) and SMIC (China).

Wafers

Main article: wafer (semiconductor)A typical wafer is made out of extremely pure silicon that is grown into mono-crystalline cylindrical ingots (boules) up to 300 mm (slightly less than 12 inches) in diameter using the Czochralski process. These ingots are then sliced into wafers about 0.75 mm thick and polished to obtain a very regular and flat surface.

Once the wafers are prepared, many process steps are necessary to produce the desired semiconductor integrated circuit. In general, the steps can be grouped into two major parts:

Processing

In semiconductor device fabrication, the various processing steps fall into four general categories: deposition, removal, patterning, and modification of electrical properties.

- Deposition is any process that grows, coats, or otherwise transfers a material onto the wafer. Available technologies consist of physical vapor deposition (PVD), chemical vapor deposition (CVD), electrochemical deposition (ECD), molecular beam epitaxy (MBE) and more recently, atomic layer deposition (ALD) among others.

- Removal processes are any that remove material from the wafer either in bulk or selectively and consist primarily of etch processes, either wet etching or dry etching. Chemical-mechanical planarization (CMP) is also a removal process used between levels.

- Patterning covers the series of processes that shape or alter the existing shape of the deposited materials and is generally referred to as lithography. For example, in conventional lithography, the wafer is coated with a chemical called a photoresist. The photoresist is exposed by a stepper, a machine that focuses, aligns, and moves the mask, exposing select portions of the wafer to short wavelength light. The unexposed regions are washed away by a developer solution. After etching or other processing, the remaining photoresist is removed by plasma ashing.

- Modification of electrical properties has historically consisted of doping transistor sources and drains originally by diffusion furnaces and later by ion implantation. These doping processes are followed by furnace anneal or in advanced devices, by rapid thermal anneal (RTA) which serve to activate the implanted dopants. Modification of electrical properties now also extends to reduction of dielectric constant in low-k insulating materials via exposure to ultraviolet light in UV processing (UVP).

Modern chips have up to eleven metal levels produced in over 300 sequenced processing steps.

Front-end-of-line (FEOL) processing

Main article: FEOLFEOL processing refers to the formation of the transistors directly in the silicon. The raw wafer is engineered by the growth of an ultrapure, virtually defect-free silicon layer through epitaxy. In the most advanced logic devices, prior to the silicon epitaxy step, tricks are performed to improve the performance of the transistors to be built. One method involves introducing a straining step wherein a silicon variant such as silicon-germanium (SiGe) is deposited. Once the epitaxial silicon is deposited, the crystal lattice becomes stretched somewhat, resulting in improved electronic mobility. Another method, called silicon on insulator technology involves the insertion of an insulating layer between the raw silicon wafer and the thin layer of subsequent silicon epitaxy. This method results in the creation of transistors with reduced parasitic effects.

Gate oxide and implants

Front-end surface engineering is followed by: growth of the gate dielectric, traditionally silicon dioxide (SiO2), patterning of the gate, patterning of the source and drain regions, and subsequent implantation or diffusion of dopants to obtain the desired complementary electrical properties. In dynamic random access memory (DRAM) devices, storage capacitors are also fabricated at this time, typically stacked above the access transistor (implementing them as trenches etched deep into the silicon surface was a technique developed by the now defunct DRAM manufacturer Qimonda).

Back-end-of-line (BEOL) processing

Main article: BEOLMetal layers

Once the various semiconductor devices have been created, they must be interconnected to form the desired electrical circuits. This occurs in a series of wafer processing steps collectively referred to as BEOL (not to be confused with back end of chip fabrication which refers to the packaging and testing stages). BEOL processing involves creating metal interconnecting wires that are isolated by dielectric layers. The insulating material was traditionally a form of SiO2 or a silicate glass, but recently new low dielectric constant materials are being used. These dielectrics presently take the form of SiOC and have dielectric constants around 2.7 (compared to 3.9 for SiO2), although materials with constants as low as 2.2 are being offered to chipmakers.

Interconnect

Historically, the metal wires consisted of aluminium. In this approach to wiring often called subtractive aluminium, blanket films of aluminium are deposited first, patterned, and then etched, leaving isolated wires. Dielectric material is then deposited over the exposed wires. The various metal layers are interconnected by etching holes, called vias, in the insulating material and depositing tungsten in them with a CVD technique. This approach is still used in the fabrication of many memory chips such as dynamic random access memory (DRAM) as the number of interconnect levels is small, currently no more than four.

More recently, as the number of interconnect levels for logic has substantially increased due to the large number of transistors that are now interconnected in a modern microprocessor, the timing delay in the wiring has become significant prompting a change in wiring material from aluminium to copper and from the silicon dioxides to newer low-K material. This performance enhancement also comes at a reduced cost via damascene processing that eliminates processing steps. As the number of interconnect levels increases, planarization of the previous layers is required to ensure a flat surface prior to subsequent lithography. Without it, the levels would become increasingly crooked and extend outside the depth of focus of available lithography, interfering with the ability to pattern. CMP (chemical mechanical planarization) is the primary processing method to achieve such planarization although dry etch back is still sometimes employed if the number of interconnect levels is no more than three.

Wafer test

The highly serialized nature of wafer processing has increased the demand for metrology in between the various processing steps. Wafer test metrology equipment is used to verify that the wafers haven't been damaged by previous processing steps up until testing. If the number of dies—the integrated circuits that will eventually become chips— etched on a wafer exceeds a failure threshold (i.e. too many failed dies on one wafer), the wafer is scrapped rather than investing in further processing.

Device test

Main article: wafer testingOnce the front-end process has been completed, the semiconductor devices are subjected to a variety of electrical tests to determine if they function properly. The proportion of devices on the wafer found to perform properly is referred to as the yield.

The fab tests the chips on the wafer with an electronic tester that presses tiny probes against the chip. The machine marks each bad chip with a drop of dye. Currently, electronic dye marking is possible if wafer test data is logged into a central computer database and chips are "binned" (i.e. sorted into virtual bins) according to predetermined test limits. The resulting binning data can be graphed, or logged, on a wafer map to trace manufacturing defects and mark bad chips. This map can be also used during wafer assembly and packaging.

Chips are also tested again after packaging, as the bond wires may be missing, or analog performance may be altered by the package. This is referred to as "final test".

Usually, the fab charges for test time, with prices in the order of cents per second. Test times vary from a few milliseconds to a couple of seconds, and the test software is optimized for reduced test time. Multiple chip (multi-site) testing is also possible, since many testers have the resources to perform most or all of the tests in parallel.

Chips are often designed with "testability features" such as scan chains and "built-in self-test" to speed testing, and reduce test costs. In certain designs that use specialized analog fab processes, wafers are also laser-trimmed during test, to achieve tightly-distributed resistance values as specified by the design.

Good designs try to test and statistically manage corners: extremes of silicon behavior caused by operating temperature combined with the extremes of fab processing steps. Most designs cope with more than 64 corners.

Die preparation

Once tested, a wafer is typically reduced in thickness

Main article: wafer backgrindingbefore the wafer is scored and then broken into individual die -- wafer dicing.

Main article: die preparationOnly the good, unmarked chips go on to be packaged.

Packaging

Main article: integrated circuit packagingPlastic or ceramic packaging involves mounting the die, connecting the die pads to the pins on the package, and sealing the die. Tiny wires are used to connect pads to the pins. In the old days, wires were attached by hand, but now purpose-built machines perform the task. Traditionally, the wires to the chips were gold, leading to a "lead frame" (pronounced "leed frame") of copper, that had been plated with solder, a mixture of tin and lead. Lead is poisonous, so lead-free "lead frames" are now mandated by ROHS.

Chip-scale package (CSP) is another packaging technology. A plastic dual in-line package, like most packages, is many times larger than the actual die hidden inside, whereas CSP chips are nearly the size of the die. CSP can be constructed for each die before the wafer is diced.[2]

The packaged chips are retested to ensure that they were not damaged during packaging and that the die-to-pin interconnect operation was performed correctly. A laser etches the chip's name and numbers on the package.

List of steps

This is a list of processing techniques that are employed numerous times in a modern electronic device and do not necessarily imply a specific order.

- Wafer processing

- Wet cleans

- Photolithography

- Ion implantation (in which dopants are embedded in the wafer creating regions of increased (or decreased) conductivity)

- Dry etching

- Wet etching

- Plasma ashing

- Thermal treatments

- Rapid thermal anneal

- Furnace anneals

- Thermal oxidation

- Chemical vapor deposition (CVD)

- Physical vapor deposition (PVD)

- Molecular beam epitaxy (MBE)

- Electrochemical Deposition (ECD). See Electroplating

- Chemical-mechanical planarization (CMP)

- Wafer testing (where the electrical performance is verified)

- Wafer backgrinding (to reduce the thickness of the wafer so the resulting chip can be put into a thin device like a smartcard or PCMCIA card.)

- Die preparation

- Wafer mounting

- Die cutting

- IC packaging

- Die attachment

- IC Bonding

- Wire bonding

- Thermosonic Bonding

- Flip chip

- Wafer bonding

- Tab bonding

- IC encapsulation

- Baking

- Plating

- Lasermarking

- Trim and form

- IC testing

Hazardous materials

Many toxic materials are used in the fabrication process[3]. These include:

- poisonous elemental dopants such as arsenic, antimony and phosphorus

- poisonous compounds like arsine, phosphine and silane

- highly reactive liquids, such as hydrogen peroxide, fuming nitric acid, sulfuric acid and hydrofluoric acid

It is vital that workers not be directly exposed to these dangerous substances. The high degree of automation common in the IC fabrication industry helps to reduce the risks of exposure of this sort. Most fabrication facilities employ exhaust management systems, such as wet scrubbers, combustors, heated absorber cartridges etc., to control the risk to workers and also the environment if these toxic materials are released into the atmosphere.

See also

Context (and History)

- Electronic design automation

- Foundry (electronics)

- Information technology

- International Technology Roadmap for Semiconductors

- Semiconductor consolidation

Wafers

- Microfabrication

- Semiconductor Equipment and Materials International (SEMI) — the semiconductor industry trade association

Integrated circuit design

- Built-in self-test

- CAD

- Hardware description language

- Computer simulation

- SPICE

- GDS II

- OASIS (Open Artwork System Interchange Standard)

Processing (and equipment)

- Laminar flow cabinets

Wafer test

Die test

Die preparation

Packaging

Hazardous materials

References

Further reading

- Kaeslin, Hubert (2008), Digital Integrated Circuit Design, from VLSI Architectures to CMOS Fabrication, Cambridge University Press, section 14.2.

External links

Categories:

Wikimedia Foundation. 2010.