- Instruction cycle

-

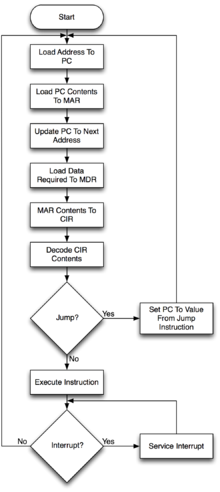

An instruction cycle (sometimes called fetch-and-execute cycle, fetch-decode-execute cycle, or FDX) is the basic operation cycle of a computer. It is the process by which a computer retrieves a program instruction from its memory, determines what actions the instruction requires, and carries out those actions. This cycle is repeated continuously by the central processing unit (CPU), from bootup to when the computer is shut down.

Contents

Circuits used

The circuits used in the CPU during the cycle are:

- Program Counter (PC) - an incrementing counter that keeps track of the memory address of which instruction is to be executed next...

- Memory Address Register (MAR) - holds the address of a memory block to be read from or written to

- Memory Data Register (MDR) - a two-way register that holds data fetched from memory (and ready for the CPU to process) or data waiting to be stored in memory

- Instruction register (IR) - a temporary holding ground for the instruction that has just been fetched from memory

- Control Unit (CU) - decodes the program instruction in the IR, selecting machine resources such as a data source register and a particular arithmetic operation, and coordinates activation of those resources

- Arithmetic logic unit (ALU) - performs mathematical and logical operations

The time period during which one instruction is fetched from memory and executed when a computer is given an instruction in machine language. There are typically four stages of an instruction cycle that the CPU carries out: 1) Fetch the instruction from memory. 2) "Decode" the instruction. 3) "Read the effective address" from memory if the instruction has an indirect address. 4) "Execute" the instruction.

Instruction cycle

Each computer's CPU can have different cycles based on different instruction sets, but will be similar to the following cycle:

1. Fetch the instruction

The next instruction is fetched from the memory address that is currently stored in the Program Counter (PC), and stored in the Instruction register (IR). At the end of the fetch operation, the PC points to the next instruction that will be read at the next cycle.

Clock Pulse: T0-T1

2. Decode the instruction

The decoder interprets the instruction. During this cycle the instruction inside the IR (instruction register) gets decoded.

Clock Pulse: T2

3. Read the effective address

In case of a memory instruction (direct or indirect) the execution phase will be in the next clock pulse. If the instruction has an indirect address, the effective address is read from main memory, and any required data is fetched from main memory to be processed and then placed into data registers(Clock Pulse: T3). If the instruction is direct, nothing is done at this clock pulse. If this is an I/O instruction or a Register instruction, the operation is performed (executed) at clock Pulse: T3.

Clock Pulse: T3

4. Execute the instruction

The CU passes the decoded information as a sequence of control signals to the relevant function units of the CPU to perform the actions required by the instruction such as reading values from registers, passing them to the ALU to perform mathematical or logic functions on them, and writing the result back to a register. If the ALU is involved, it sends a condition signal back to the CU.

Clock Pulse: T3-T6 (Up to T6)

The result generated by the operation is stored in the main memory, or sent to an output device. Based on the condition of any feedback from the ALU, Program Counter may be updated to a different address from which the next instruction will be fetched.

The cycle is then repeated.

Initiating the cycle

The cycle starts immediately when power is applied to the system using an initial PC value that is predefined for the system architecture (in Intel IA-32 CPUs, for instance, the predefined PC value is

0xfffffff0). Typically this address points to instructions in a read-only memory (ROM) which begin the process of loading the operating system. (That loading process is called booting.)[1]Fetch cycle

Step 1 of the Instruction Cycle is called the Fetch Cycle. These steps are the same for each instruction. The fetch cycle processes the instruction from the instruction word which contains an opcode.

Decode

Step 2 of the instruction Cycle is called the decode. The opcode fetched from the memory is being decoded for the next steps and moved to the appropriate registers.

Read the effective address

Step 3 is deciding which operation it is. If this is a Memory operation - in this step the computer checks if it's a direct or indirect memory operation:

- Direct memory instruction - Nothing is being done.

- Indirect memory instruction - The effective address is being read from the memory.

If this is a I/O or Register instruction - the computer checks it's kind and execute the instruction.

Execute cycle

Step 4 of the Instruction Cycle is the Execute Cycle. These steps will change with each instruction.

The first step of the execute cycle is the Process-Memory. Data is transferred between the CPU and the I/O module. Next is the Data-Processing uses mathematical operations as well as logical operations in reference to data. Central alterations is the next step, is a sequence of operations, for example a jump operation. The last step is a combined operation from all the other steps.

The Fetch-Execute cycle in Transfer Notation

Expressed in register transfer notation:

![MAR\gets [PC]](8/3188648e7501a0e6df7dc87a5f59fc43.png)

![MDR\gets [Memory]_{MAR address}; PC\gets [PC]+1](7/9670f479efc347f685b7d41957c031a2.png) (Increment the PC for next cycle at the same time)

(Increment the PC for next cycle at the same time)![IR\gets [MDR]](2/cb2773dc5cc6ae795b0c7cd2148d898c.png)

The registers used above, besides the ones described earlier, are the Memory Address Register (MAR) and the Memory Data Register (MDR), which are used (at least conceptually) in the accessing of memory. Often, the MDR is expressed as the MBR (Memory Buffer Register).Fetch and execute example (written in RTL - Register Transfer Language):

PC=0x5AF , AC=0x7EC3 , M[0x5AF]=0x932E , M[0x32E]=0x09AC , M[0x9AC]=0x8B9F.

T0 : AR = 0x5AF (PC)

T1 : IR = 0x932E (M[AR]) , PC=0x5BO

T2 : DECODE = ADD opCode 0x932E , AR=0x32E , I=1. (Indirect instruction)

T3 : AR = 0x9AC (M[AR])

T4 : DR = 0x8B9F

T5 : AC = 0x8B9F + 0x7EC3 = 0x0A62, E = 1 (carry out) , SC = 0Summary: this example is for an ADD Instruction which made Indirect where:

T0-T1 is the Fetch operation.

T2 is the operation code Decode.

T3 Indirect Memory reference

T4-T5 Execute ADD operationReferences

- ^ Bosky Agarwal (2004). "Instruction Fetch Execute Cycle". http://www.cs.montana.edu/~bosky/cs518/ife/IFE.pdf. Retrieved 2010-07-09.[dead link]

Categories:- Instruction processing

Wikimedia Foundation. 2010.