- Crossbar latch

-

The cross-bar latch is a technology invented by Hewlett-Packard in October 2001, that potentially could replace transistors in some applications. Transistors are essential components of logic gates and memory cells in digital electronic systems. The historical trend for computer systems to become smaller and more powerful over the years is mostly due to techniques for producing ever smaller transistors. The memristor devices that make up a cross bar latch potentially can be made far smaller than any transistor.

The crossbar was introduced by Hewlett-Packard scientists in the Journal of Applied Physics, and allows much the same functionality of transistors, except on a molecular scale. It has been seen by many[who?] as an advancement as far above the transistor as the latter was to the vacuum tube. The crossbar latch consists of a signal line crossed by two control lines. Depending on the voltages sent down the various lines, it can simulate the action of the three major logic gates: AND, OR and NOT.

The abstract of the patent is as follows:

"A molecular crossbar latch is provided, comprising two control wires and a signal wire that crosses the two control wires at a non-zero angle to thereby form a junction with each control wire. Each junction forms a switch and the junction has a functional dimension in nanometers. The signal wire selectively has at least two different voltage states, ranging from a 0 state to a 1 state, wherein there is an asymmetry with respect to the direction of current flow from the signal wire through one junction compared to another junction such that current flowing through one junction into (out of) the signal wire can open (close) while current flowing through the other junction out of (into) the signal wire can close (open) the switch, and wherein there is a voltage threshold for switching between an open switch and a closed switch. Further, methods are provided for latching logic values onto nanowires in a logic array, for inverting a logic value, and for restoring a voltage value of a signal in a nano-scale wire. Invented by Phillip J Kuekes."

— U.S. patent 6,586,965

Contents

Applications in arithmetic processing

Two main approaches exist for the application of crossbar latches as components of arithmetic processing devices.

The first approach was developed by Greg Snider of Hewlett-Packard and employs crossbar latches to replicate the functions of a half adder, which form the basis of modern computational architectures.[1] In this approach a crossbar tile is formed of a layer of horizontal row wires and a layer of vertical column wires in which memristor or similar materials are sandwiched between the horizontal and vertical wire layers. Each intersection or junction of the crossbar tile is configurable to be at a high-resistance state in which there is little or no current between the horizontal and vertical wires or at a low-resistance state in which current is permitted. Fig. 1 illustrates the configuration of a half-adder using a crossbar tile, as taught by Snider, with the nodes identifying junctions of the crossbar tile configured as low-resistance states. By setting different logic inputs A, NOT A, B, and NOT B to different row wires this configuration produces the sum and carry outputs typical for a half-adder. Connections between multiple half-adders may then be used to form full adders in accordance with conventional arithmetic architectures.

The second approach was described at the 2008 NSTI Nanotechnology Conference[2] and combines crossbar latches with analog processing circuitry. This approach has the primary advantage of reducing the number of crossbar latch tiles necessary for arithmetic processing but may ultimately be limited in processing speed and precision due to the inclusion of analog circuit components. In order to perform computation this configuration takes advantage of the reconfigurability of crossbar latches and uses multiple programming iterations of the crossbar latches to perform binary arithmetic. For example, in Figs. 2A–2C each vertical wire of the column array represents a different binary bit significance value (1, 2, 4, 8, etc.) and binary numerical values are stored in each row using high resistance states to represent logic 0 and low resistance states to represent logic 1. Fig. 2A demonstrates performing the addition 1+2+3+4 by initially configuring the crossbar rows with corresponding binary resistance states 0001, 0010, 0011, and 0100.

Summing amplifiers and analog to digital converters are used to sum the low-resistance states in each column, producing the analog outputs 0, 1, 2, 2. These analog values are converted to their binary equivalents 00, 01, 10, 10, which are then used to reconfigure the crossbar array for a second iteration as illustrated in Fig. 2B. In the second iteration the placement of the reconfiguration bits are in accordance with the bit significance of the output column in the first iteration and the binary outputs in this case are 00,10,01,00.

In the third iteration, since at most one bit per column is in the low-conductance state the output the A/D converters produce only two possible states which correspond to the expected result (1+2+3+4=10=1010(base-2)).

In a related patent application[3] this process is described to be scaled up to 127-bit arithmetic processes including multiplication and division.

Applications of crossbar latch in neuromorphics

Crossbar latches have been suggested as components of neuromorphic computing systems. One implementation of this is in the form of a neural network formed from nanowires as discussed in a patent by Greg Snider of Hewlett-Packard[4]. At the third international conference on Nano-Networks [5] another implementation was proposed using analog circuitry and a memristor based crossbar configuration. As illustrated below the intersected wires of crossbar latches are formed to sandwich memristor material so as to generate variable resistance elements (M1-M4) tunable between a low resistance state (RL) and high resistance state (RH) and are connected to an operational amplifier circuit which functions to sum input voltage signals V1(t)-V4(t) based on the state of the memristance materials at the intersections of the crossbar wires. One of the key advantages of such systems is that they integrate both memory and processing functions in a single circuit and thus avoid the delays inherent to conventional processor designs which separate the memory from the processor. This could prove useful to future designs of electronics for pattern recognition systems.

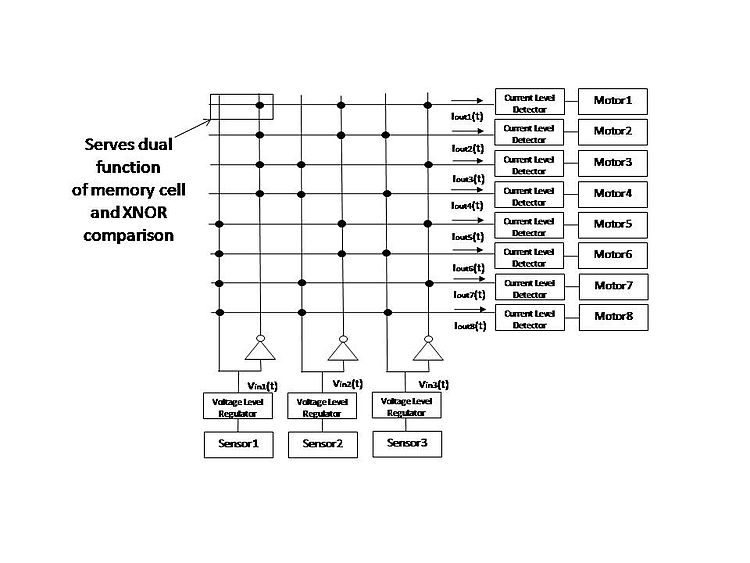

Applications of crossbar latch array in pattern recognition

At the 2nd International Multi-Conference on Engineering and Technological Innovation a crossbar latch circuit architecture was described for pattern recognition based on memristors.[6] The circuit design used the crossbar latch structures to store resistance data patterns which were compared to sensed voltage patterns input to the crossbar columns. Each crossbar latch performed dual functions of memory storage and an XNOR comparison function to produce an analog row output current having a magnitude related to the similarity between the stored resistance pattern and the sensed voltage patterns. Depending on the binary voltage states of the sensors a different row produces current to drive a particular motor. The advantage of this design was explained to overcome the bottleneck of the Von Neumann architecture by integrating memory storage and data processing in a common circuit.

See also

External links

- U.S. Patent 6,586,965

- Research could send transistors the way of the vacuum tube (HP Press Release)

- HP claims molecular computing breakthrough (ComputerWorld)

- HP's 'Crossbar Latch' to Replace Transistors? (InterNetNews)

References

- ^ "U.S. Patent 7,203,789". http://www.google.com/patents?id=zrB_AAAAEBAJ&dq=7203789,.

- ^ Mouttet, B. (2008-07-05). "Logicless Computational Architectures with Nanoscale Crossbar Arrays". NSTI Nanotech 2008 Conference. http://www.nsti.org/Nanotech2008/showabstract.html?absno=119. Retrieved 2008-07-05.

- ^ "U.S. Patent Application 11/395,232". http://www.google.com/patents?id=kGShAAAAEBAJ&dq=11/395,232,.

- ^ "U.S. Patent 7,359,888". http://www.google.com/patents?id=4wupAAAAEBAJ&dq=7359888,.

- ^ "Nano-Net 2008". http://www.nanonets.org/.

- ^ Mouttet, Blaise L (2009). "Memristor Pattern Recognition Circuit Architecture for Robotics". Proceedings of the 2nd International Multi-Conference on Engineering and Technological Innovation II: 65–70. http://www.iiis2009.org/imeti/program/HTML/program-20.htm

Categories:- Electrical components

Wikimedia Foundation. 2010.