- Memory geometry

-

In the design of modern personal computers, memory geometry describes the internal structure of random-access memory. Memory geometry is of concern to consumers upgrading their computers, since older memory controllers may not be compatible with later products. Memory geometry terminology can be confusing because of the number of overlapping terms.

Contents

Physical features

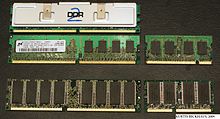

Top L-R, DDR2 with heat-spreader, DDR2 without heat-spreader, SO-DIMM DDR2, DDR, SO-DIMM DDR

Memory geometry describes the logical configuration of a RAM module, but consumers will always find it easiest to grasp the physical configuration. Much of the confusion surrounding memory geometry occurs when the physical configuration obfuscates the logical configuration. The first defining feature of RAM is form factor. RAM modules can be in compact SO-DIMM form for space constrained applications like laptops, printers, embedded computers, and small form factor computers, and in DIMM format, which is used in most desktops.

The other physical characteristic determine with by physical examination are the number of memory chips, and whether both sides of the memory "stick" are populated. If 4 is a factor of the number of memory devices or chips (or more generally, a power of two), then the module does not feature ECC, if 9 is a factor of the number of memory chips (or one more than a power of two), then the module does. RAM modules are 'keyed' by indentations on the sides, and along the bottom of the module. This determines the technology, and classification of the modules, for instance whether it is DDR2, or DDR3, and whether it is suitable for desktops, or for servers. It is important to make sure that the keying of the module matches the key of the slot it is intended to occupy. Additional, non-memory chips on the module are an indication that it could be designed for high capacity memory systems for servers, and that the module may be incompatible with desktop systems.

As the next section of this article will cover the logical architecture, which covers the logical structure spanning every populated slot in a system, the physical features of the slots themselves becomes important. By consulting the documentation of your motherboard, or reading the labels on the board itself, you can determine the underlying logical structure of the slots. When there is more than one slot, they are numbered, and when there is more than one channel, the different slots are separated in that way as well - usually color-coded.

Logical features

In the 90s specialized computers were released where two computers that each had their own memory controller could be networked at such a low level that the software run could use the memory, or CPU of either computer as if they were one unit. With AMD's release of the Opteron, and Intel's corresponding systems systems that share more than one memory controller in a single system have become common in applications that require the power of more than one common desktop. For these systems schemes like Non-Unified Memory Architecture are used.

Channels are the highest level structure at the local memory controller level. Modern computers can have two, three or even more channels. It is usually important that, for each module in any one channel, there is a logically identical module in the same location on each of the other populated channels.

Module capacity is the aggregate space in a module measured in byte, or - more generally - in words. Module capacity is equal to the product of the rank density and the number of ranks, and where the rank density is the product of rank depth, and rank width[1]. The standard format for expressing this specification is (rank density) Mbit x (rank width)x(number of ranks).

Banks are one of the chief sources of physical/logical confusion. Banks are a logical distinction that corresponds to CSRows in low level addressing, for more details on the addressing of RAM in this POV, see dynamic random access memory. As memory density has increased, the numbers of ranks in each chip has also increased. As an example of a simple configuration, say there is one module with 8 chips, or devices, on each side, and one rank in each of the 16 chips, and each bank was 8 bits wide, that module would have one bank for each side. One bank on one side, and one bank on the back. Today you could have a module composed of Micron Technology MT47H128M16 chips with the organization 16Mb x 16 x 8 with a bank width of 16. With a module which has of 8 of those on each side, there would be 2 "x16" "banks" on each side. Memory controllers such as the Intel 945 Chipset list the configurations they support: "Supports 256-Mb, 512-Mb, and 1-Gb DDR2 technologies for x8 and x16 devices." "Supports four banks for all DDR2 devices up to 512-Mbit density. Supports eight banks for 1-Gbit DDR2 devices." As an example, take an i945 memory controller with 4 Kingston KHX6400D2/1Gs.

Kingston describes each module as having a geometry of 128Mx64, meaning that each one has 64 bits 128 million deep, equaling 8.192 billion bits, or 1.024 Gigabytes. Kingston describes each "device", or chip as having a geometry of 64Mx8, so each module has four banks. So from the MCH point of view when there are 4 1GB modules, it sees 2 channels, each with 8 banks.

Hierarchy of organization

Memory chip

The lowest form of organization covered by memory geometry, sometimes called "memory device". These are the component ICs that make up each module, or module of RAM. The most important measurement of a chip is its density, measured in bits. Because memory bus width is usually larger than the number of chips, most chips are designed to have width, meaning that they are divided into equal parts internally, and when one address "depth" is called up, instead of returning just one value, more than one value is returned. In addition to the depth, a second addressing dimension has been added at the chip level, banks. Banks allow one bank to be available, while another bank is unavailable because it is refreshing. An example of chip notation is 64Mb (depth) X 8 (width) X 8 Banks.

Memory module

Some measurements of modules are size, width, speed, and latency. A memory module consists of a multiple of the memory chips to equal the desired module width. So a 32-bit SIMM module could be composed of four 8-bit wide (x8) chips. As noted in the memory channel part, one physical module can be made up of one or more logical ranks. If that 32-bit SIMM were composed of eight 8-bit chips the SIMM would have two ranks. An example of Module notation is 128 Mb x 64-bit.

Memory channel

A memory channel is made up of ranks. Physically a memory channel with just one memory module might present itself as having one or more logical ranks.

Controller organization

This is the highest level. In a typical computer there will only be a single memory controller with only one or two channels. The logical features section described NUMA configurations, which can take the form of a network of memory controllers. For example, each socket of a two socket AMD K8 can have a two channel memory controller, giving the system a total of four memory channels.

See also

- DIMM

- List of device bandwidths

- Dynamic random access memory

- Random-access memory

- Memory organisation

- Memory address

- Memory bank

- Bank switching

- Double-sided RAM

- Dual-channel architecture

- Page address register

References

- http://www.kingston.com/tools/umg/pdf/umg.pdf

- http://ixbtlabs.com/articles2/mainboard/ram-faq-2006.html

- http://www.rampedia.com/index.php/faq

- http://arstechnica.com/paedia/r/ram_guide/ram_guide.part1-1.html

- http://www.pcguide.com/ref/ram/packBanks-c.html

- http://www.valueram.com/datasheets/KHX6400D2_1G.pdf

- http://www.intel.com/Assets/PDF/datasheet/307502.pdf

Categories:- Computing terminology

- Computer memory

Wikimedia Foundation. 2010.